近日,韩国延世大学Kim等人提出一种简单、低温、可溶液加工且可扩展的策略,通过调整和利用Sn基钙钛矿的氧化现象来制造高性能增强型JFETs。通过形成p型PEA₂SnI₄和n型IGZO之间的PN结,利用Sn基钙钛矿的氧化表面层有效抑制栅极漏电流,实现增强型操作模式,这种结构被称为阻挡型JFET(b-JFET)。该b-JFET拥有优异的电气性能,包括29.4 cm²/Vs的场效应迁移率、67.1 mV/dec低SS以及在≤1V操作电压下超过10⁵的开关电流比。此外,尽管其包含通常不稳定的Sn钙钛矿层,该器件在环境空气中仍展现出强大的环境、偏置和操作稳定性。该研究成果以题为“Revisiting the role of oxidation in stable and high-performance lead-free perovskite-IGZO junction field-effect transistors” 发表于Nature Communications期刊。

技术亮点:

Ø氧化层的利用:Sn基钙钛矿氧化表面层可以被用来提高晶体管性能,而不是完全抑制这种氧化;

Ø 阻挡层的形成:通过控制Sn基钙钛矿的氧化过程,形成“阻挡层”,有效抑制栅极漏电流,实现增强型操作模式;

Ø高性能JFETs:该b-JFET实现优异电气性能,包括29.4 cm²/Vs的场效应迁移率、67.1 mV/dec低SS以及在≤1V操作电压下超过10⁵的开关电流比;

Ø环境稳定性:尽管其包含通常不稳定的Sn钙钛矿层,该器件在环境空气中展现出强大的环境、偏置和操作稳定性;

Ø 逻辑电路的构建:通过构建逻辑电路并实现高反相增益值,进一步证实该器件在各种实际应用中的潜力。

研究意义:

该工作提出基于Sn基钙钛矿氧化的b-JFET为高性能、低功耗的电子设备提供了一种新的解决方案。该器件在环境空气中展现出强大的稳定性,并成功构建了逻辑电路。与传统的基于晶体管的电路相比,该架构在面积、延迟和能耗方面实现显著的改进,为边缘计算中的空间-时间信息感知提供新的可能性。

图文分析:

钙钛矿b-JFET工作机理

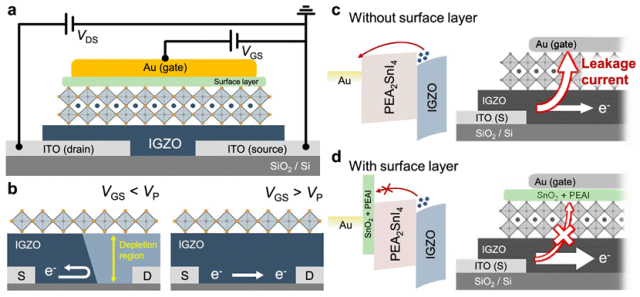

图1 钙钛矿双极结型场效应晶体管(b-JFET)的工作机制。a,b 基于PEA2SnI4/IGZO异质结的钙钛矿b-JFET结构示意图及工作原理图示;c,d 器件内部电子流动示意图以及氧化处理前后钙钛矿b-JFET的对应能带图。

钙钛矿b-JFET电气性能

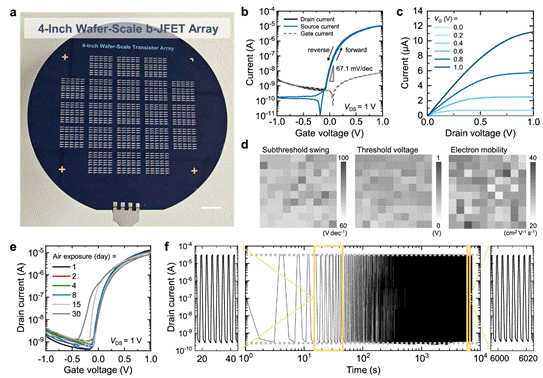

图2. a 四英寸晶圆级钙钛矿b-JFET阵列的光学图像(比例尺1厘米);b 优化后器件的转移特性曲线;c 优化后器件的输出特性曲线;d 亚阈值摆幅、阈值电压和有效场效应迁移率分布的二维彩色映射图;e 优化后器件的空气稳定性测试结果;f 钙钛矿b-JFET的工作稳定性测量数据。

氧化层表征

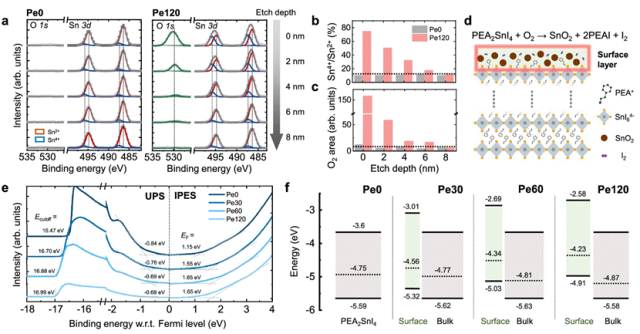

图3. a Pe0 和 Pe120 的 XPS 深度分析图谱;b, c 从 Sn 3d XPS 谱峰反卷积计算得到的 Pe0 和 Pe120 中 Sn⁴⁺ 与 Sn²⁺ 的比例,以及 Pe0 和 Pe120 的 O 面积;d PEA₂SnI₄氧化时的化学反应示意图;e 不同退火时间的PEA₂SnI₄薄膜的 UPS 和 IPES 分析结果;f 不同退火时间的PEA₂SnI₄薄膜的表面和体相能带图。

TCAD模拟

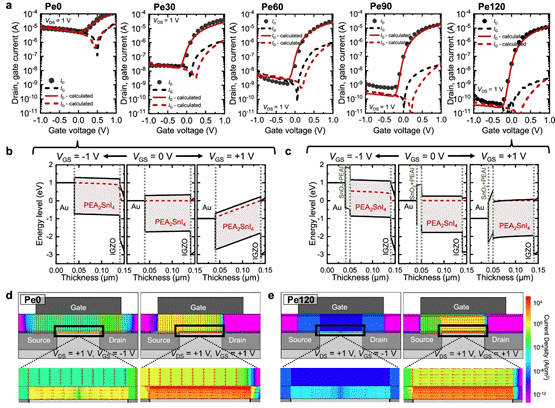

图4 . a 不同退火时间钙钛矿双极结型场效应晶体管(b-JFET)的实验与仿真转移特性曲线;b Pe0基与c Pe120基钙钛矿b-JFET在不同栅源电压(VGS)下的能带图;d Pe0基与e Pe120基钙钛矿b-JFET在VGS为−1V(左图)和1V(右图)时的二维电流密度分布TCAD仿真图。

逻辑门电路

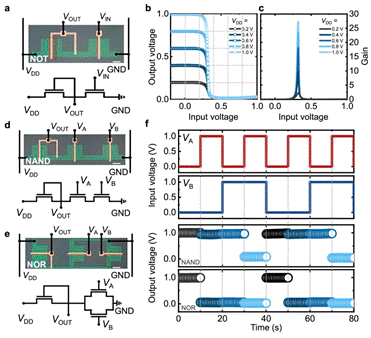

图5. a NOT门的光学显微图像及对应电路图(比例尺=500μm);b NOT门在不同VDD下的电压传输特性与c增益特性;d,e NAND门与NOR门在VDD=1V时的光学显微图像及电路图(比例尺=500μm);f NAND门和NOR门在四种逻辑组合(0,0)、(1,0)、(0,1)、(1,1)下的输出电压对应关系。。

实验细节

通过低温溶液加工方法制备高性能增强型结型场效应晶体管(b-JFET)。首先,对Si/SiO₂(300nm)衬底进行清洗后,通过射频磁控溅射沉积30nm厚的ITO层,并在空气中600°C下退火30分钟。随后,在ITO层上通过射频磁控溅射沉积10nm厚的IGZO层,并在450°C下退火5分钟,接着通过光刻和化学蚀刻对IGZO层进行图案化。接着,通过化学气相沉积(CVD)在IGZO层上沉积2.5μm厚的Parylene-c层,并进行光刻和反应离子刻蚀以形成硬掩模。之后,将PEA₂SnI₄前驱体溶液旋涂在Parylene-c层上,并在100°C下退火10分钟。通过机械剥离去除Parylene-c层后,将PEA₂SnI₄层暴露在60°C、约40%相对湿度的空气中进行120分钟的热处理,形成氧化表面层。最后,通过热蒸发在钙钛矿层上沉积40nm厚的金层作为电极,并通过CVD在器件上沉积1μm厚的Parylene-c层进行封装。

文献来源:

Kim S, Kim S H, Hwang H U, et al. Revisiting the role of oxidation in stable and high-performance lead-free perovskite-IGZO junction field-effect transistors. Nature Communications(2025).

https://doi.org/10.1038/s41467-025-62770-2.

仅用于学术分享,如有侵权,请联系删除。

索比光伏网 https://news.solarbe.com/202509/09/50008117.html